# Firmware Multiplier

Prof. Alberto Borghese Dipartimento di Informatica

borghese@di.unimi.it

Università degli Studi di Milano

Riferimenti sul Patterson 5a ed.: B.6 & 3.4

A.A. 2023-2024 1/41 http:\\borghese.di.unimi.it\

## Sommario

Il moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

## L'approccio firmware

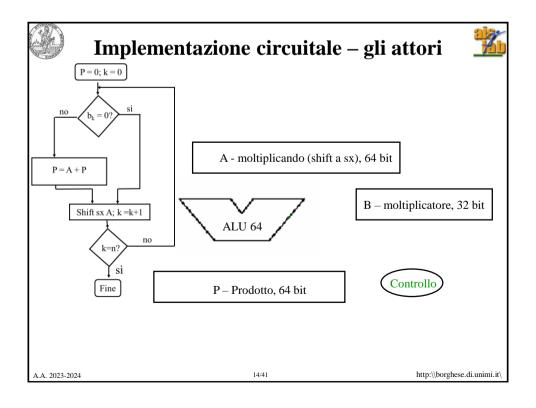

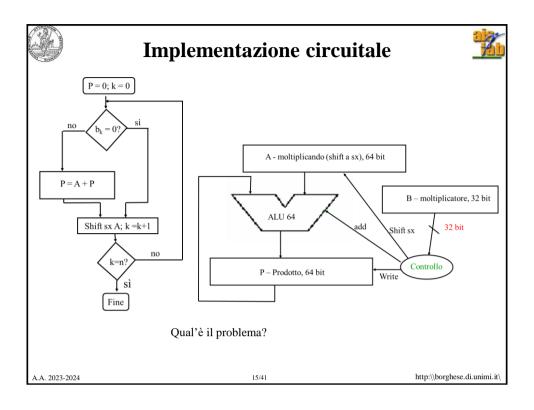

Nell'approccio firmware, viene inserita nella ALU una micro-architettura costituita da una unità di controllo, dei componenti di calcolo e dei registri.

L'unità di controllo attiva opportunamente le unità di calcolo e il trasferimento da/verso i registri. Approccio "controllore-datapath" in piccolo.

Viene inserito un microcalcolatore dentro la ALU.

Il primo microprogramma era presente nell'IBM 360 (1964).

A.A. 2023-2024 3/41 http:\\borghese.di.unimi.it\

## L'approccio firmware vs hardware

La soluzione HW è più veloce ma più costosa per numero di porte e complessità dei circuiti. Inoltre è rigida («hard») e non si può adattare a implementare funzioni diverse

La soluzione firmware risolve l'operazione complessa mediante una sequenza di operazioni semplici. E' meno veloce, ma più flessibile e, potenzialmente, adatta ad inserire nuove procedure, modificando solamente l'unità di controllo.

La soluzione HW viene utilizzata per le operazioni frequenti: la velocizzazione di operazioni complesse che vengono utilizzate raramente non aumenta significativamente le prestazioni (legge di Amdahl).

A.A. 2023-2024 4/41 http:\\borghese.di.unimi.it\

### Approcci tecnologici alla ALU

Quattro approcci tecnologici alla costruzione di una ALU (e di una CPU):

- Approccio porte logiche. E' un approccio esaustivo (tabellare). Per ogni funzione, per ogni ingresso viene memorizzata l'uscita. E' utilizzabile per funzioni molto particolari (ad esempio di una variabile). Non molto utilizzato.

- Approccio hardware programmabile (e.g. PLA, FPGA). Ad ogni operazione corrisponde un circuito combinatorio specifico.

- Approccio firmware (firm = stabile), o microprogrammato. Si dispone di circuiti specifici solamente per alcune operazioni elementari (tipicamente addizione e sottrazione). Le operazioni più complesse vengono sintetizzate collegando opportunamente i componenti, a partire dall'algoritmo che le implementa.

A.A. 2023-2024 5/41 http:\\borghese.di.unimi.it\

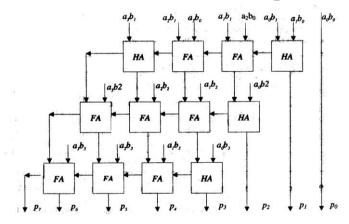

## Circuito hardware della moltiplicazione

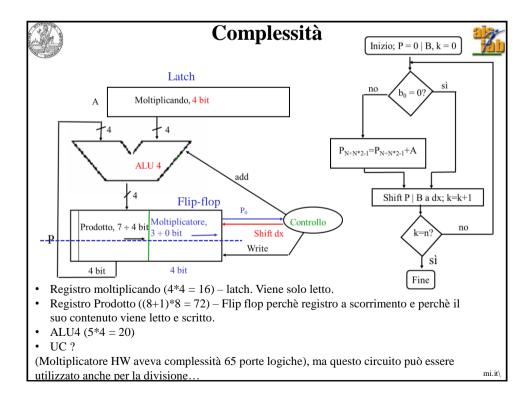

Complessità<sub>t</sub> = (N-2) \* [(N-1)\*5+1\*2] + (N-2)\*5+2\*2 + N\*NComplessità per parole su 4 bit = 2\*(3\*5+2)+14+16=64 porte a due ingressi

Come possiamo renderlo più flessibile? Come arrivare a un circuito che serva anche la divisione intera?

A.A. 2023-2024 6/41 http:\\borghese.di.unimi.it\

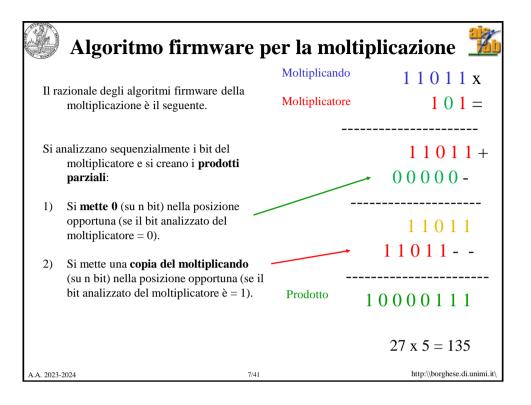

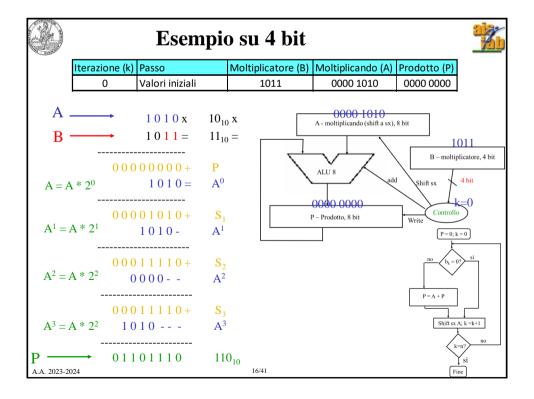

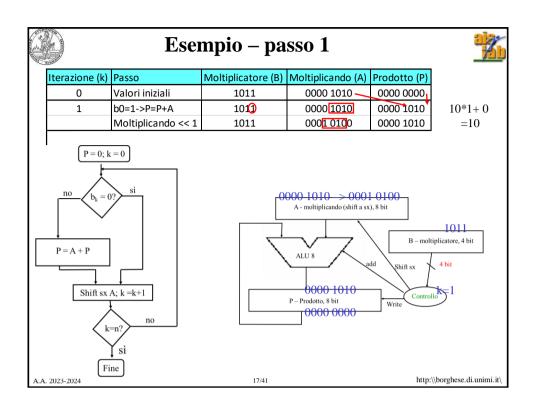

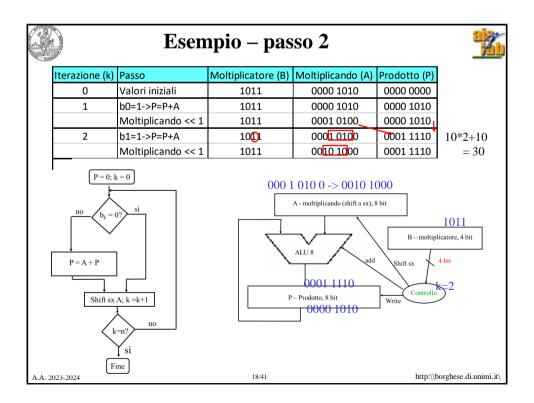

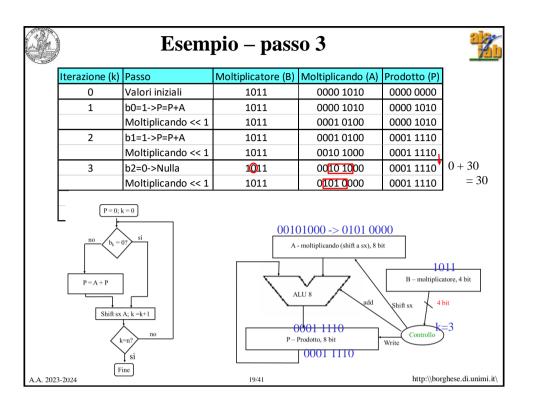

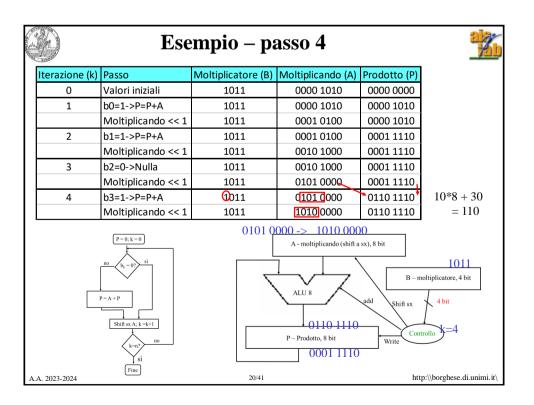

# Esempio – riassunto

| Iterazione (k) | Passo              | Moltiplicatore (B) | Moltiplicando (A)        | Prodotto (P) |

|----------------|--------------------|--------------------|--------------------------|--------------|

| 0              | Valori iniziali    | 1011               | 0000 1010 —              | 0000 0000    |

| 1              | b0=1->P=P+A        | 1011               | 0000 1010                | 0000 1010    |

|                | Moltiplicando << 1 | 1011               | 000 <mark>1 010</mark> 0 | 0000 1010    |

| 2              | b1=1->P=P+A        | 1001               | 000 <mark>1.010</mark> 0 | 0001 1110    |

|                | Moltiplicando << 1 | 1011               | 00 <mark>10 10</mark> 00 | 0001 1110    |

| 3              | b2=0->Nulla        | 1011               | 00 <mark>10 10</mark> 00 | 0001 1110    |

|                | Moltiplicando << 1 | 1011               | 01010000                 | 0001 1110    |

| 4              | b3=1->P=P+A        | <b>(1)</b> 011     | 0 <mark>101 (</mark> 000 | 0110 1110    |

|                | Moltiplicando << 1 | 1011               | 1010 0000                | 0110 1110    |

#### **Esercizi**

Costruire il circuito HW che esegui la moltiplicazione 7 x 9 in base 2 su 4 bit.

Eseguire la stessa moltiplicazione secondo l'algoritmo visto, indicando passo per passo il contenuto dei 3 registri: A che contiene il moltiplicando, B che contiene il moltiplicatore e P che contiene somme parziali ed il risultato finale.

#### **Sommario**

#### I moltiplicatori firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2023-2024 23/41 http://borghese.di.unimi.it/

| Iterazione (k) | Passo              | Moltiplicatore (B)  | Moltiplicando (A)        | Prodotto (P) |

|----------------|--------------------|---------------------|--------------------------|--------------|

| 0              | Valori iniziali    | 1011                | 0000 1010 —              | 0000 0000    |

| 1              | b0=1->P=P+A        | 101(1)              | 0000 1010                | 0000 1010    |

|                | Moltiplicando << 1 | 1011                | 0001 0100                | 0000 1010    |

| 2              | b1=1->P=P+A        | 10 <mark>0</mark> 1 | 0001 0100                | 0001 1110    |

|                | Moltiplicando << 1 | 1011                | 00 <mark>10 10</mark> 00 | 0001 1110    |

| 3              | b2=0->Nulla        | 1011                | 00 <mark>10 10</mark> 00 | 0001 1110    |

|                | Moltiplicando << 1 | 1011                | 0101 0000                | 0001 1110    |

| 4              | b3=1->P=P+A        | <b>①</b> 011        | Q <mark>101 Q</mark> 000 | 0110 1110    |

|                | Moltiplicando << 1 | 1011                | 1010 0000                | 0110 1110    |

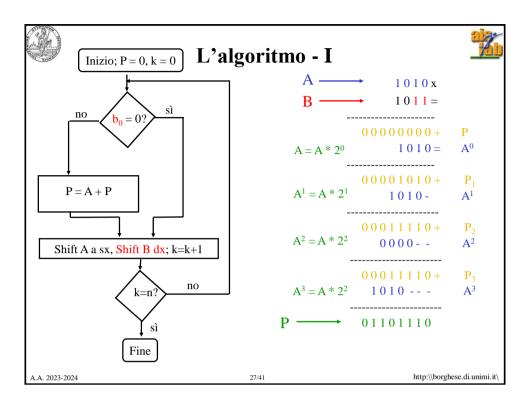

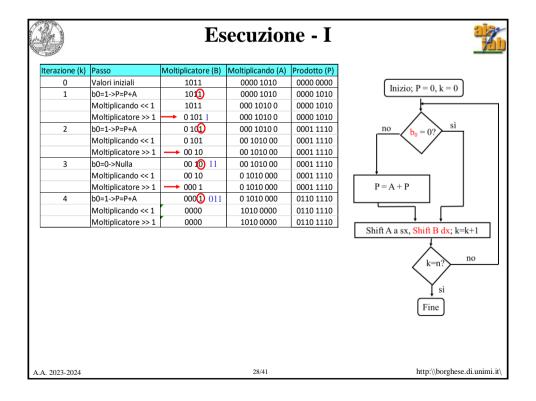

Ottimizzazione

- Inizializzo B (ho tutti i bit di B)

- A ogni passo leggo B, ma utilizzo solo 1 bit, b<sub>k</sub>

- Utilizzo b<sub>k</sub> a ogni iterazione, **poi non serve più**.

- Non è necessario conservare tutti i bit di B per tutta la durata dell'operazione.

Situazione del tipo: **produttore-consumatore**.

Produco dei dati: la parola B.

Consumo i dati: 1 bit della parola B a ogni iterazione (consume = utilizzo una tantum e non riutilizzo in seguito.

24/41 http://borghese.di.unimi.it/

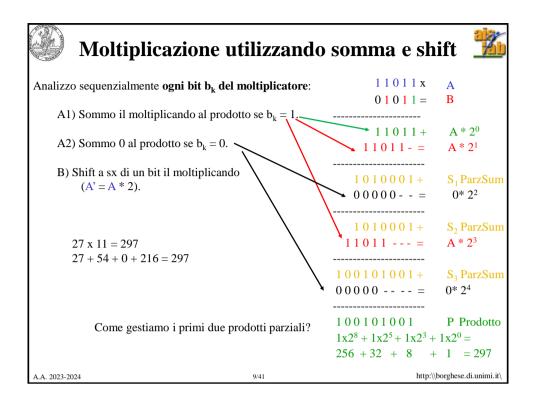

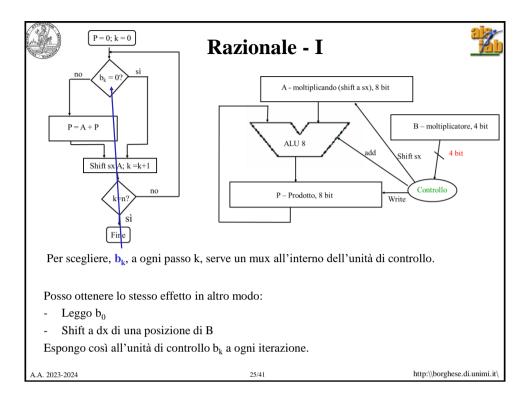

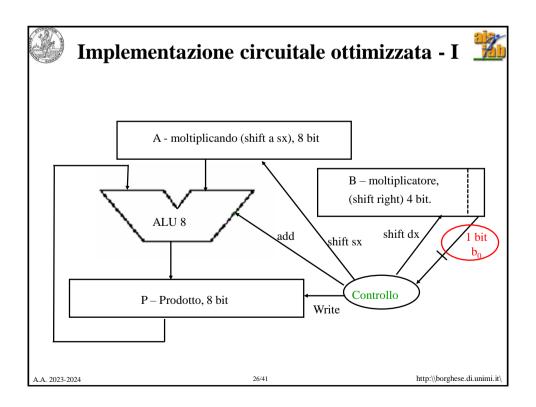

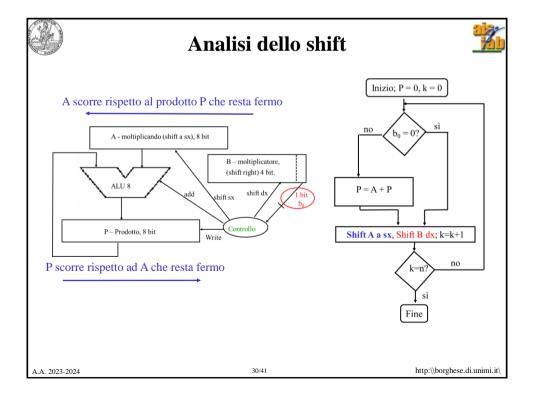

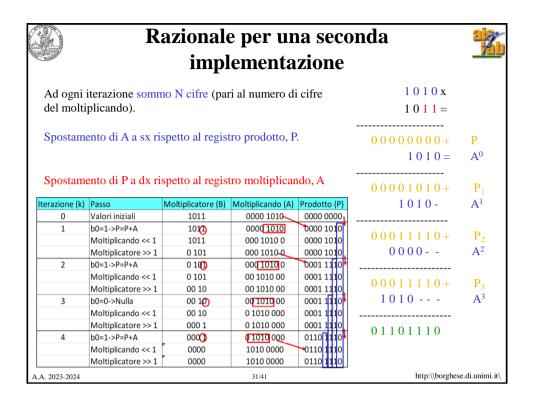

# Razionale per una seconda implementazione

Meta' dei bit del registro moltiplicando vengono utilizzati a ogni iterazione.

Gli N bit del moltiplicando sommati al registro prodotto vengono incolonnati di una posizione più a sinistra a ogni iterazione. Occupano N bit.

Ad ogni iterazione 1 bit del registro prodotto viene calcolato definitivamente.

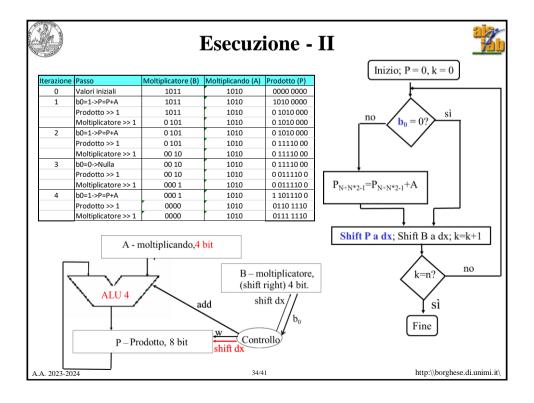

| Iterazione (k) | Passo               | Moltiplicatore (B) | Moltiplicando (A) | Prodotto (P) |

|----------------|---------------------|--------------------|-------------------|--------------|

| 0              | Valori iniziali     | 1011               | 0000 1010         | 0000 0000    |

| 1              | b0=1->P=P+A         | 1017)              | 0000 1010         | 0000 1010    |

|                | Moltiplicando << 1  | 1011               | 000 1010 0        | 0000 1010    |

|                | Moltiplicatore >> 1 | 0 101              | 000 1010 0        | 0000 1010    |

| 2              | b0=1->P=P+A         | → 01 <b>①</b>      | 000 1010 0        | 0001 1110    |

|                | Moltiplicando << 1  | 0 101              | 00 1010 00        | 0001 1110    |

|                | Moltiplicatore >> 1 | 00 10              | 00 1010 00        | 0001 1110    |

| 3              | b0=0->Nulla         | 00 10              | 00 1010 00        | 00011110     |

|                | Moltiplicando << 1  | 00 10              | 0 1010 000        | 0001 1110    |

|                | Moltiplicatore >> 1 | 000 1              | 0 1010 000        | 0001 1110    |

| 4              | b0=1->P=P+A         | → 0003             | 0 1010 000        | 01101110     |

|                | Moltiplicando << 1  | 0000               | 1010 0000         | 0110 1110    |

|                | Moltiplicatore >> 1 | 0000               | 1010 0000         | 0110 1110    |

1010+ 1 010 . = 1 111 . + 00 00 . . 01 11 . . + 101 0 . . . 110 1 . . .

A.A. 2023-2024 29/41 http:\\borghese.di.unimi.it\

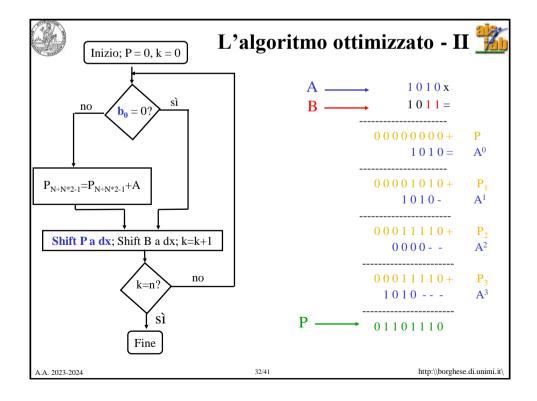

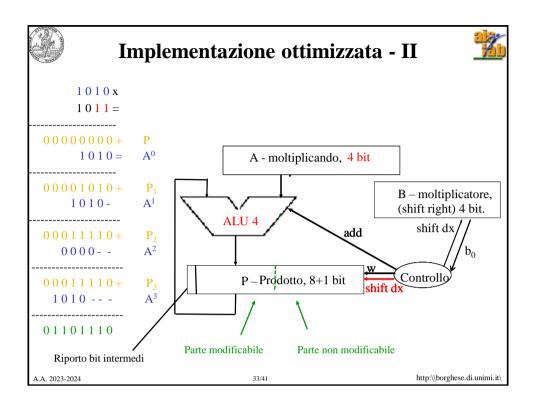

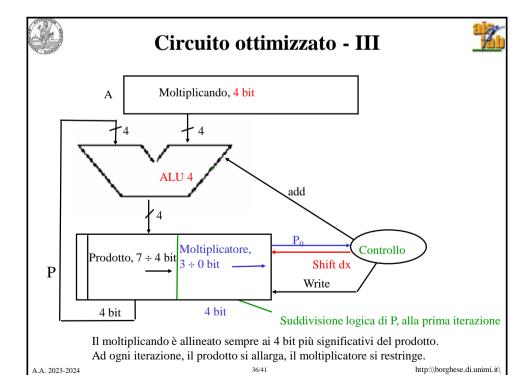

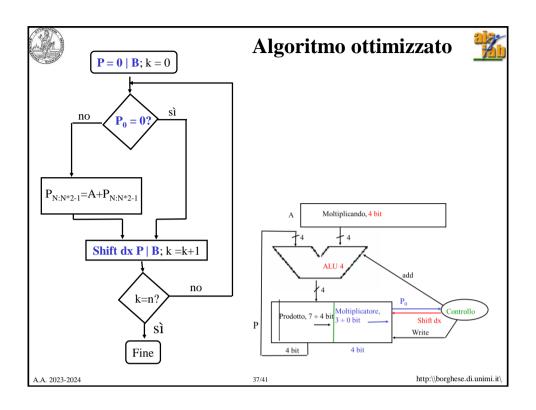

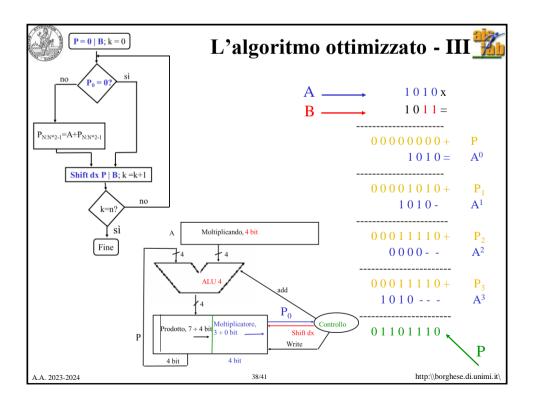

# Razionale dell'implementazione - III

Il numero di bit del registro **prodotto** corrente (somma dei prodotti parziali) più il numero di bit da esaminare nel registro **moltiplicatore** rimane costante ad ogni iterazione (pari a 8 bit).

Si può perciò eliminare il registro moltiplicatore.

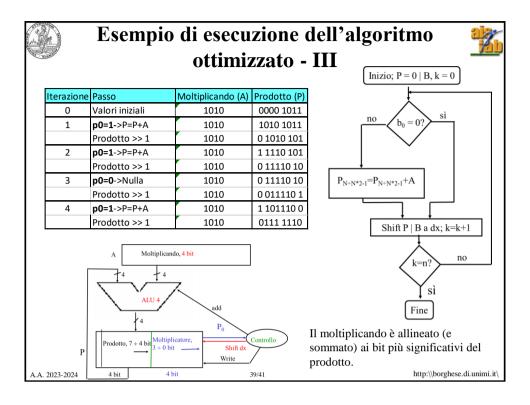

| Iterazione | Passo               | Moltiplicatore (B) | Moltiplicando (A) | Prodotto (P) |

|------------|---------------------|--------------------|-------------------|--------------|

| 0          | Valori iniziali     | 1011               | 1010              | 0000 0000    |

| 1          | b0=1->P=P+A         | 1011               | 1010              | 1010 0000    |

|            | Prodotto >> 1       | 1011               | 1010              | 0 1010 000   |

|            | Moltiplicatore >> 1 | 0 101              | 1010              | 0.1010 000   |

| 2          | b0=1->P=P+A         | 0 101              | 1010              | 1 1110 000   |

|            | Prodotto >> 1       | 0 101              | 1010              | 0 11110 00   |

|            | Moltiplicatore >> 1 | 00 10              | 1010              | 0 11110 00   |

| 3          | b0=0->Nulla         | 00 10              | 1010              | 0 11110 00   |

|            | Prodotto >> 1       | 00 1 <u>0</u>      | 1010              | 0 011110 0   |

|            | Moltiplicatore >> 1 | 000 1              | 1010              | 0 011110 0   |

| 4          | b0=1->P=P+A         | 000 1              | 1010              | 1 101110 0   |

|            | Prodotto >> 1       | 0000               | 1010              | 0110 1110    |

|            | Moltiplicatore >> 1 | 0000               | 1010              | 0111 1110    |

A.A. 2023-2024 http://borghese.di.unimi.it/

# Sommario

I moltiplicatori firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2023-2024 41/41 http://borghese.di.unimi.it/